數位電子/邏輯非或

外觀

< 數位電子

非或門是兩種基本邏輯閘之一(另一種是與非門),任何其他邏輯閘都可以用它們來構建。由於這種特性,非或門和與非門有時被稱為“通用門”。但是,現代積體電路並不完全由單一型別的門構建。相反,EDA 工具用於將邏輯電路的描述轉換為複雜門的網表(標準單元)或電晶體(全定製方法)。

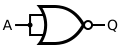

非門是透過連線非或門的輸入而製成的。由於非或門相當於一個或門後接一個非門,因此連線非或門的輸入只留下非門部分。

| 所需門 | 非或門結構 | ||||||

|---|---|---|---|---|---|---|---|

|

| ||||||

| |||||||

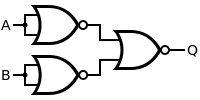

如果檢查非或門的真值表,或應用德摩根定律,可以發現,如果任何輸入為 0,那麼輸出將為 1。但是,要成為與門,只有當兩個輸入都為 1 時,輸出才為 1。因此,如果輸入被反轉,兩個高輸入將觸發高輸出。

| 所需門 | 非或門結構 | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||||||

| |||||||||||||||||||||

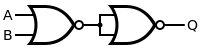

或門簡單地是一個輸出反轉的非或門(一個非門)。非門只是輸入連線在一起的非或門。因此,兩個非或門的級聯,第二個非或門的輸入連線在一起,將產生一個或門。

| 所需門 | 非或門結構 | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||||||

| |||||||||||||||||||||

與非門可以透過反轉與門的輸出來實現。

| 所需門 | 非或門結構 | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||||||

| |||||||||||||||||||||

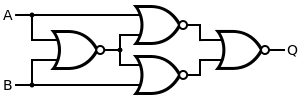

異或門使用五個非或門構建。其中三個門以與門拓撲連線。此排列的邏輯表示式為 ((A 且 B) 非或 (A 非或 B))。

| 所需門 | 非或門結構 | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||||||

| |||||||||||||||||||||

異或非門是透過連線四個非或門製成的,如下所示。這實際上代表了公式:(A 非或 (A 非或 B)) 非或 (B 非或 (A 非或 B))。

| 所需門 | 非或門結構 | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||||||

| |||||||||||||||||||||

- Floyd, Thomas, L. (1997), Digital Fundamentals (6th ed.), Englewood Cliffs, NJ: Prentice-Hall, ISBN 0133984885.