微處理器設計/ALU

微處理器通常具有一個模組,用於對整數執行算術運算。這是因為許多不同的算術和邏輯運算可以使用類似(如果不是相同)的硬體來執行。執行算術和邏輯運算的元件稱為算術邏輯單元,或 ALU。 [1]

ALU 是微處理器中最重要的元件之一,通常是處理器中首先設計的部件。設計完 ALU 後,就可以實現微處理器的其餘部分,以將運算元和控制程式碼提供給 ALU。

ALU 單元通常需要能夠執行基本邏輯運算(AND、OR)和加法運算。在輸入端包含反相器使相同的 ALU 硬體能夠執行減法運算(新增反相運算元)以及 NAND 和 NOR 運算。

基本 ALU 設計包括一個“ALU 切片”集合,每個切片都可以對單個位執行指定的操作。每個運算元的每個位都有一個 ALU 切片。

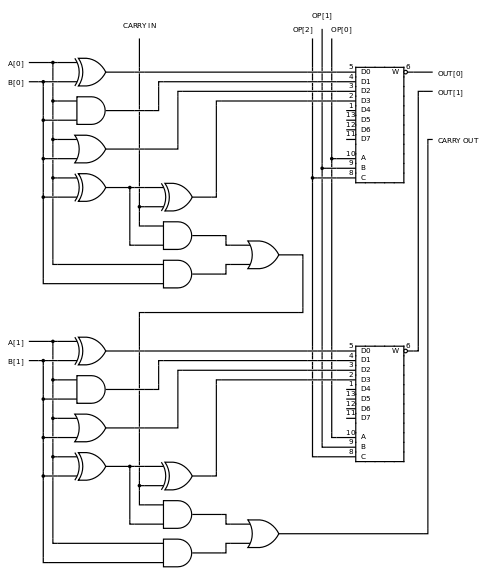

這是一個基本的 2 位 ALU 示例。影像右側的框是多路複用器,用於選擇各種操作:OR、AND、XOR 和加法。

請注意,所有操作都是並行執行的,選擇訊號 (“OP”) 用於確定將哪個結果傳遞到資料路徑的其餘部分。請注意,進位訊號(僅用於加法)是為每個操作生成的,並從 ALU 傳遞出去,因此如果我們不執行加法,就必須忽略進位標誌。

這是一個 4 位 ALU 的電路圖。

邏輯運算和加法是最簡單,也是最常見的運算。因此,典型的 ALU 被設計為專門處理這些運算,而其他運算,如乘法和除法,則在單獨的模組中處理。

還要注意,我們在此討論的 ALU 單元僅適用於整數資料型別,而不是浮點資料。幸運的是,一旦設計了整數 ALU 和乘法器單元,就可以使用這些單元來建立浮點單元 (FPU)。

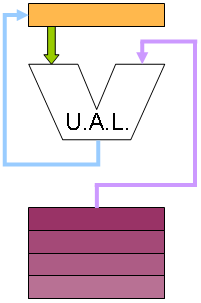

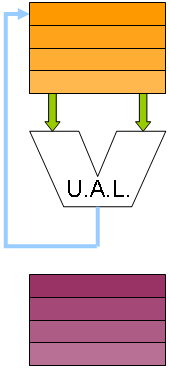

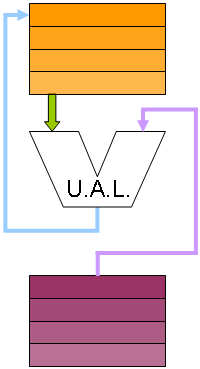

設計完 ALU 後,我們需要定義它如何與處理器的其餘部分互動。我們可以選擇多種不同的配置,每種配置都有優缺點。每個指令集架構 (ISA) 類別——堆疊、累加器、暫存器-記憶體或暫存器-暫存器-載入-儲存——都需要不同的 ALU 連線方式。 [2] 在下面的所有影像中,橙色表示 CPU 內部記憶體結構(暫存器),紫色表示外部記憶體(RAM)。

累加器機器有一個特殊的暫存器,稱為累加器。累加器儲存每個 ALU 操作的結果,並且也是每個指令的運算元之一。這意味著我們的 ISA 可以更簡單,因為指令只需要指定一個運算元,而不是兩個運算元和一個目標。累加器架構具有簡單的 ISA,並且通常非常快,但是需要編寫額外的軟體才能將正確的值載入到累加器中。不幸的是,累加器機器很難進行流水線處理。

常見臺式計算器可能是使用累加器的一種計算機系統型別。

更常見的架構之一是暫存器到暫存器架構,也稱為 3 個暫存器運算元機器。在此配置中,程式設計師可以指定兩個源運算元和一個目標暫存器。不幸的是,ISA 需要擴充套件以包含兩個源運算元和目標運算元的欄位。這需要更長的指令字長,並且與累加器相比,還需要額外的努力才能在執行後將結果寫回暫存器檔案。此寫回步驟會導致流水線處理器中的同步問題(我們將在後面討論流水線)。

暫存器堆疊類似於暫存器到暫存器和累加器結構的組合。在暫存器堆疊中,ALU 從堆疊頂部讀取運算元,並將結果壓入堆疊頂部。複雜的數學運算需要分解為逆波蘭式,這對於程式設計師來說可能很難使用。但是,許多計算機語言編譯器可以輕鬆地生成逆波蘭式,因為內部使用二叉樹來表示指令。此外,還需要建立硬體來實現暫存器堆疊,包括 PUSH 和 POP 操作,以及硬體來檢測和處理堆疊錯誤(壓入已滿的堆疊或彈出空堆疊)。

好處來自高度簡化的 ISA。這些機器被稱為“0 運算元”或“零地址機器”,因為不需要指定運算元,因為所有操作都作用於指定的堆疊位置。

在右側的圖中,“SP” 是指向堆疊頂部的指標。這只是實現堆疊結構的一種方式,儘管它可能是最簡單的方式之一。

一種複雜的結構是暫存器和記憶體結構,如左側所示。在此結構中,一個運算元來自暫存器檔案,另一個運算元來自外部記憶體。在此結構中,ISA 很複雜,因為每個指令字都需要能夠儲存一個完整的記憶體地址,這可能非常長。在實踐中,這種方案不會直接使用,而是通常會整合到其他方案中,例如暫存器到暫存器方案,以提高靈活性。

一些 CISC 架構可以選擇將指令的一個運算元指定為記憶體地址,儘管它們通常被指定為暫存器地址。

還有許多其他結構可用,其中一些是新穎的,另一些是上面列出的型別的組合。設計人員需要決定如何構建微處理器,以及如何將資料饋送到 ALU。

英特爾 IA-32 指令集架構 (x86 處理器) 在浮點運算單元中使用暫存器堆疊架構,但在整數運算中使用修改後的暫存器到暫存器結構。所有整數運算都可以指定一個暫存器作為第一個運算元,以及一個暫存器或記憶體位置作為第二個運算元。第一個運算元充當累加器,結果儲存在第一個運算元暫存器中。這種架構的缺點是指令字長度不統一,這意味著處理器中的指令提取和解碼模組需要非常複雜。

典型的 IA-32 指令寫成以下形式:

ADD AX, BX

ADD AX, BX

例子: MIPS

[edit | edit source]MIPS 使用暫存器到暫存器結構。每個運算都可以指定兩個暫存器運算元,以及一個第三個目標暫存器。缺點是記憶體讀取需要在單獨的運算中進行,指令字的小格式意味著空間很寶貴,某些任務難以執行。

MIPS 指令的示例如下:

ADD R1, R2, R3

ADD R1, R2, R3

參考資料

[edit | edit source]- ↑ CPU 設計師使用各種名稱來稱呼算術邏輯單元,包括“ALU”、“整數執行單元”和“E-box”。Paul V. Bolotoff. "快取儲存器功能原理" 2007.

- ↑ "指令集原理:基本 ISA 類別" by Dr. Sofiène Tahar