微處理器設計/流水線處理器

讓我們將我們的微處理器分解成 5 個不同的活動,這些活動通常對應於 5 個不同的硬體部分

- 指令獲取 (IF)

- 指令解碼 (ID)

- 執行 (EX)

- 記憶體讀寫 (MEM)

- 結果回寫 (WB)

任何給定的指令在任何時候都只需要其中一個模組,通常按照這個順序。下面的多週期處理器時序圖將更詳細地展示這一點

這一切都很好,但在任何時刻,5 個單元中有 4 個處於非活動狀態,可能可以用於其他事情。

流水線處理以下任務

- 使用多週期方法來減少單個週期中的計算量。

- 每個週期的計算量更少,允許更快的時鐘週期。

- 指令重疊允許處理器的所有元件都在不同的指令上執行。

- 透過更頻繁地完成指令來提高吞吐量。

我們將在本章的剩餘部分討論如何實現這些目標。

鑑於我們的多週期處理器,如果我們想讓我們的執行重疊,以便同時處理多達 5 條指令,該怎麼辦?讓我們稍微縮短一下我們的時序圖來展示這個想法

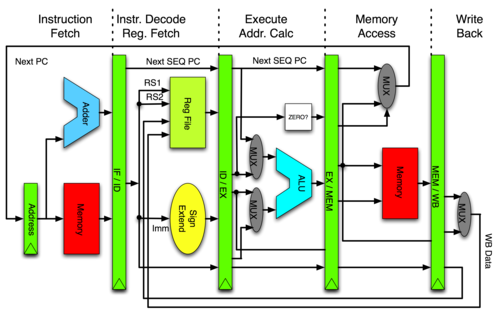

如該圖所示,處理器中的每個元素在每個週期都處於活動狀態,處理器的指令速率提高了 5 倍!現在的問題是,為了執行這項任務,我們需要什麼額外的硬體?我們需要在每個流水線狀態之間新增儲存暫存器以儲存週期之間的部分結果,我們還需要重新引入單週期 CPU 中的冗餘硬體。我們可以繼續使用單個記憶體模組(用於指令和資料),只要我們將記憶體讀取操作限制在週期的前半部分,並將記憶體寫入操作限制在週期的後半部分(反之亦然)。我們可以透過在上一階段計算記憶體地址來節省記憶體訪問時間。

暫存器需要儲存該點流水線的資料,以及操作剩餘流水線所需的控制程式碼。

我們得到的處理器設計將類似於以下內容

如果我們有 5 條指令,我們可以使用不同的顏色在我們的流水線中顯示它們。在下圖中,白色對應於 NOP,不同的顏色對應於流水線中的其他指令。每個階段,指令都會在流水線中向前移動。

流水線處理器在執行相同軟體時,會生成與一次執行一條指令的處理器相同的結果——只是它們生成這些結果的速度快得多。構建流水線處理器的工程師有時會新增特殊的硬體——運算元轉發;流水線互鎖;等等——為了獲得“就像”每條指令都被獲取、評估,並且它的結果在獲取下一條指令之前就被提交(非重疊)的相同結果——儘管流水線處理器實際上是重疊指令的。

處理器的吞吐量是指一段時間內完成的指令數量。許多處理器被設計成具有每時鐘週期一條指令的典型吞吐量,即使任何特定指令都需要多個週期——每個流水線階段一個週期——從獲取到完成的時間。

超級流水線是一種提高流水線深度以提高時鐘速度並減少各個階段延遲的技術。如果 ALU 的執行時間是其他任何模組的三倍,我們可以將 ALU 分成三個獨立的階段,這將減少在較短階段上浪費的時間。這裡的問題是,我們需要找到一種方法將我們的階段細分為更短的階段,我們還需要構建更復雜的控制單元來操作流水線並防止所有可能的危險。

現代高階處理器擁有超過 20 個流水線階段並不少見。

- Jim Plusquellic. "CMSC 611: Advanced Computer Architecture". "流水線簡介".

- Jon "Hannibal" Stokes. "流水線:概述(第一部分)".

- Jon Stokes. "流水線:概述(第二部分)".