實用電子學/加法器

加法器是一種將兩個位相加並輸出結果的裝置。被加在一起的位稱為“加數”。加法器可以串聯在一起,以便將任意長度的兩個二進位制數相加。

加法器有兩種 - 半加器和全加器。半加器只是將兩個位相加並給出兩個位的輸出。全加器將兩個輸入和來自另一個加法器的進位輸入相加,並也給出兩個位的輸出。

將兩個獨立的位加在一起時,有四種可能的組合。每種組合都在左側顯示,以及它的解。

很容易看出,當加數不同時,右邊的位(“個位”位)才是 1。因此,將加數異或在一起可以得到右邊的位。此位稱為 **和**,是加數的 模 2 和(即,如果在超過 1 後迴圈回到 0,則為解)。

左邊的位僅在兩個加數均為 1 時才為 1,因此可以使用與門來生成此位,稱為 **進位** 位。總結一下

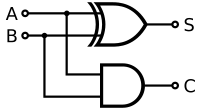

左邊的圖顯示了完整的半加器,其中加數用 A 和 B 表示,和用 S 表示,進位用 C 表示。

真值表如下(括號中的數字是位的權重 - 每個加數為 1,和也為 1 - 進位為 2)

| A (1) | B (1) | S (1) | C (2) | |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | |

| 0 | 1 | 1 | 0 | |

| 1 | 0 | 1 | 0 | |

| 1 | 1 | 0 | 1 |

半加器的缺點是,雖然它們可以生成進位輸出,但它們無法處理進位輸入訊號。這意味著它們只能是獨立的單元,並且串聯起來以新增多個位數字。

全加器透過將三個數字相加來解決這個問題 - 兩個加數與半加器中的加數相同,以及一個進位輸入。

全加器可以透過將 A 和 B 連線到一個半加器的輸入,將該半加器的和連線到第二個加法器的輸入,將進位輸入 Cin 連線到另一個輸入,並將兩個半加器進位輸出或運算以給出最終進位輸出 Cout 來構建。

下面的圖顯示了門級全加器。

此處提供了顯示兩個半加器模組輪廓的此圖的版本。此處。全加器的輸出是三個一位數字的兩位算術和。

此全加器的邏輯表示式為

透過應用布林代數,第二個語句簡化為

在三個數字的輸入中,第一個是 A 的狀態,第二個是 B 的狀態,第三個是 Cin 的狀態,下面描述了此全加器的功能

- 所有導致一個 (100, 010, 001) 的組合在和輸出處產生高電平,因為只有在第二個異或門處存在一個高電平(當 A 和 B 為低電平時,第一個門給出低電平,當 A 或 B 為高電平時,第一個門給出高電平)在和輸出處產生高電平。由於只有一個輸入始終為高電平,因此任何與門都不能變為高電平,並且進位輸出 Cout 為高電平。

- 所有導致兩個 (011, 101, 110) 的組合產生高進位輸出和低和

- 011 使第一個異或門變為高電平,因為 A 和 B 不同。結合 Cin 處的“高”電平,這使頂部的與門變為高電平,因此進位輸出也變為高電平。第二個異或門處存在兩個高電平會使和保持低電平。

- 101 的工作方式與 011 方式完全相同,因為 A 和 B 是可互換的。

- 110:A 和 B 為“高”電平迫使第一個異或門為“低”電平;此“低”電平結合 Cin 的“低”電平在和處產生“低”電平。A 和 B 的“高”電平使底部的與門變為高電平,因此 Cout 為“高”電平。

- 當輸入為 111 時,第一個異或門由於兩個高輸入而變為“低”電平,而第二個異或門變為“高”電平,因為它有一個“低”輸入(來自第一個異或門)和一個“高”輸入(來自 Cin 輸入)。這在和輸出處產生“高”電平。A 和 B 均為“高”電平會觸發底部的與門,並且進位輸出 Cout 也變為“高”電平。

全加器的真值表如下,顯示了輸入和輸出的權重

| A (1) | B (1) | Cin (1) | S (1) | Cout (2) | |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 1 | 0 | |

| 0 | 1 | 0 | 1 | 0 | |

| 0 | 1 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 1 |

如果 A 和 B 均為“高”電平,則連線到它們的與門將輸出“高”電平,但異或門將輸出“低”電平,迫使另一個與門為“低”電平。如果第一個半加器的“和”輸出為“高”電平,則 A 或 B 中必須有一個為“低”電平,這意味著連線到它們的與門被強制為“低”電平。這意味著組合兩個半加器進位輸出的或門中的兩個輸入永遠不會同時為“高”電平,此門可以用異或門替換(當兩個輸入均為“高”電平時,或門和異或門不同)。這意味著只需要兩種型別的門,並且全加器可以用兩個 IC 實現。

這些可以在級聯中執行,其中一個級的進位輸出驅動下一個級的進位輸入。這將在下一節中討論。

在上一節中,我們介紹瞭如何將兩個一位二進位制數相加,同時考慮到來自前一個二進位制數量級 (BOOM) 的任何進位以及進位到下一個 BOOM 的任何進位。透過將這些一位加法器串聯起來,我們可以製作一個加法器來新增任意長度的二進位制數。

為此,將第一級進位輸入連線到地,因為在最低有效位之前沒有進位。然後將第一級進位輸出連線到下一級的進位輸入,依此類推,您可以使用任意多的級。

以下是 4 位加法器的佈局

請注意,只有在進位輸出依次在每個級中註冊後,結果才會完整。這種級聯效應是這種加法器被稱為 **行波進位加法器** 的原因。這需要一點時間,對於大型(32 位或更多)加法器,它可能需要幾百納秒,如果需要高速,這可能是個問題。

有一些速度更快的加法器可以製造,它們沒有級聯效應,例如 進位超前加法器。

IC 實現

[edit | edit source]The 4008 IC 是一個 4 位全加器,它可以依次與其他加法器串聯起來,以提供任意長度的數字。