實用電子學/觸發器

觸發器是一種存在於兩種狀態之一的電路,因此可以儲存資訊。簡單的觸發器可以用一對與非邏輯閘來定義。觸發器是非線性電路,這意味著其中一個門的輸出被反饋回以與輸入訊號一起處理。因為觸發器在與這個先前輸出訊號混合的輸入訊號上執行,所以它們自己的輸出依賴於它們之前狀態。

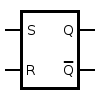

觸發器(F/F)是由數字門組成的一種裝置,它使用反饋來儲存其輸入的狀態(1或0)。觸發器經常被用來鎖存輸入資料。這意味著觸發器“記住”它的二進位制資料,直到被告知“忘記”它。所有觸發器至少有一個標記為Q的輸出。經常他們有一個標記為/Q的補碼。4種基本的觸發器是RS、D、反轉和JK觸發器

配置 數學表示式 真值表

Q = R + Q_

Q_ = S + QSR QQ 00 XX 01 01 10 10 11 00

Q = R . Q_

Q_ = S . QSR QQ 00 00 01 01 10 10 11 XX

最基本的鎖存器是簡單的SR觸發器,其中S和R分別代表置位和復位。它可以用一對交叉耦合的非門來構建。儲存的位出現在標記為Q的輸出端。

通常,在儲存模式下,S和R輸入都為低電平,反饋保持Q和Q輸出處於恆定狀態,其中Q是Q的補碼。如果S(置位)在R保持為低電平的情況下被脈衝至高電平,那麼Q輸出將被強制為高電平,並且即使S返回低電平後也會保持高電平;類似地,如果R(復位)在S保持為低電平的情況下被脈衝至高電平,那麼Q輸出將被強制為低電平,並且即使R返回低電平後也會保持低電平。

| SR觸發器操作[1] | |||||||

|---|---|---|---|---|---|---|---|

| 特性表 | 激勵表 | ||||||

| S | R | 動作 | Q(t) | Q(t+1) | S | R | 動作 |

| 0 | 0 | 保持狀態 | 0 | 0 | 0 | X | 無變化 |

| 0 | 1 | Q = 0 | 0 | 1 | 1 | 0 | 置位 |

| 1 | 0 | Q = 1 | 1 | 0 | 0 | 1 | 復位 |

| 1 | 1 | 不穩定組合, |

1 | 1 | X | 0 | 無變化 |

('X'表示“不關心”條件;這意味著訊號無關緊要)

Q輸出始終在時鐘上升沿到來時取D輸入的狀態。(或者如果時鐘輸入為低電平有效,則取下降沿)[2] 因此它被稱為D觸發器,因為輸出取D輸入或資料輸入的值,並將其延遲一個時鐘計數。D觸發器可以解釋為原始的儲存單元、零階保持器或延遲線。

真值表

時鐘 D Q Qprev 上升沿 0 0 X 上升沿 1 1 X 非上升沿 X Qprev

('X'表示不關心條件,這意味著訊號無關緊要)

這些觸發器非常有用,因為它們構成了移位暫存器的基礎,而移位暫存器是許多電子裝置的重要組成部分。與D型鎖存器相比,D觸發器的優勢在於它在時鐘變為高電平時“捕獲”訊號,並且資料線的後續變化不會影響Q,直到下一個上升沿到來。例外情況是,一些觸發器有一個“復位”訊號輸入,它會復位Q(為零),並且可以是非同步的,也可以是與時鐘同步的。

上面的電路將暫存器的內容向右移動,每次時鐘的有效躍遷移動一位。輸入X被移入最左邊的位位置。

如果T輸入為高電平,則每當時鐘輸入被選通時,T觸發器就會改變狀態(“反轉”)。如果T輸入為低電平,則觸發器保持先前值。這種行為可以用特徵方程來描述

- (或者,在沒有異或運算子的情況下,等效的:)

並可以用真值表來描述

| T觸發器操作[1] | ||||||||

|---|---|---|---|---|---|---|---|---|

| 特性表 | 激勵表 | |||||||

| 註釋 | 註釋 | |||||||

| 0 | 0 | 0 | 保持狀態(無clk) | 0 | 0 | 0 | 無變化 | |

| 0 | 1 | 1 | 保持狀態(無clk) | 1 | 1 | 0 | 無變化 | |

| 1 | 0 | 1 | 反轉 | 0 | 1 | 1 | 補碼 | |

| 1 | 1 | 0 | 反轉 | 1 | 0 | 1 | 補碼 | |

當T保持為高電平時,反轉觸發器將時鐘頻率除以二;也就是說,如果時鐘頻率為4 MHz,從觸發器獲得的輸出頻率將為2 MHz。這種“除以”特性在各種型別的數字計數器中都有應用。T觸發器也可以用JK觸發器(J & K引腳連線在一起並充當T)或D觸發器(T輸入和Qprevious透過異或門連線到D輸入)來構建。

JK觸發器有2個標記為J和K的輸入,以及一個CLK輸入(用三角形標記),它由一系列1和0饋送。 和 是互補的,還有SET(S)和RESET(R)輸入。 [3]

JK 觸發器是對 SR 觸發器(J=置位,K=復位)行為的擴充套件,它將 S = R = 1 的條件解釋為“翻轉”或切換命令。具體來說,組合 J = 1,K = 0 是將觸發器置位的命令;組合 J = 0,K = 1 是將觸發器復位的命令;組合 J = K = 1 是將觸發器切換的命令,即將其輸出更改為其當前值的邏輯補碼。將 J = K = 0 設定為不會產生 D 觸發器,而是保持當前狀態。要合成 D 觸發器,只需將 K 設定為 J 的補碼。因此,JK 觸發器是一種通用觸發器,因為它可以配置為 SR 觸發器、D 觸發器或 T 觸發器。注意:觸發器是正邊沿觸發(時鐘脈衝),如時序圖所示。

JK 觸發器的特徵方程為

相應的真值表為

| JK 觸發器操作 [1] | ||||||||

|---|---|---|---|---|---|---|---|---|

| 特性表 | 激勵表 | |||||||

| J | K | Qnext | 註釋 | Q | Qnext | J | K | 註釋 |

| 0 | 0 | 保持狀態 | 0 | 0 | 0 | X | 無變化 | |

| 0 | 1 | 復位 | 0 | 1 | 1 | X | 置位 | |

| 1 | 0 | 置位 | 1 | 0 | X | 1 | 復位 | |

| 1 | 1 | 反轉 | 1 | 1 | X | 0 | 無變化 | |

注意:JK 觸發器名稱的由來由 JPL 工程師 P. L. Lindley 在給電子設計雜誌《EDN》的一封信中詳細說明。這封信的日期是 1968 年 6 月 13 日,並於當年 8 月的通訊中發表。在這封信中,Lindley 先生解釋說他從 Eldred Nelson 博士那裡聽到了 JK 觸發器的故事,Nelson 博士在休斯飛機公司工作期間負責創造了這個術語。當時休斯公司使用的觸發器都是後來被稱為 J-K 的型別。在設計邏輯系統時,Nelson 博士對觸發器的輸入分配了字母,如下所示:#1:A & B,#2:C & D,#3:E & F,#4:G & H,#5:J & K。

另一種理論認為,置位和復位輸入被賦予了“J”和“K”的符號,因為幫助設計 J-K 觸發器的工程師之一名叫 Jack Kilby。

- ↑ a b c Mano, M. Morris (2004). Logic and Computer Design Fundamentals, 3rd Edition. Upper Saddle River, NJ, USA: Pearson Education International. pp. pg283. ISBN 0-13-1911651.

{{cite book}}:|pages=has extra text (help); Unknown parameter|coauthors=ignored (|author=suggested) (help) - ↑ D 觸發器

- ↑ D.A.Godse, A.P.Godse 邏輯設計 ISBN 9788184312768