用於 FPGA 設計的 VHDL/4 位加法器

外觀

庫 ieee;使用 ieee.std_logic_1164.all;使用 ieee.std_logic_unsigned.all 使用 ieee.std_logic_arith.all;

實體 Adder4 是埠(a、b:輸入整數範圍 -8 到 7;和:輸出整數範圍 -16 到 15);結束 Adder4;

架構 Adder4arch 的 Adder4 是開始的和<=a+b;

結束 Adder4arch;

library ieee;

use ieee.std_logic_1164.all;

use work.all;

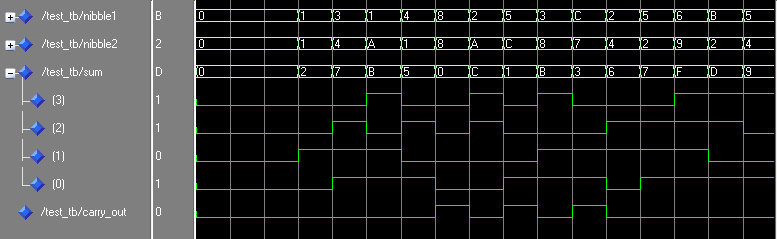

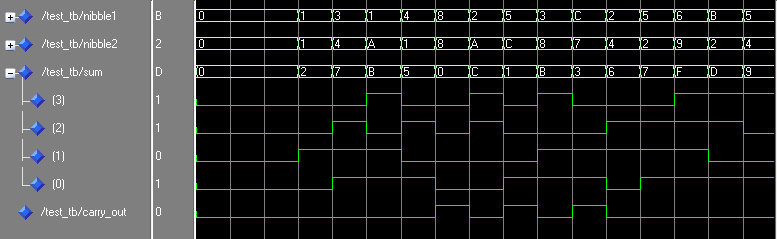

entity adder4b is

port (a,b,c:in std_logic_vector(3 downto 0);

cin:in std_logic;

cout:out std_logic;

s:out std_logic_vector(3 downto 0));

END adder4b;

architecture arch12 of adder is

signal y:std_logic_vector(4 downto 0);

begin

y(0)<= cin;

cout<=y(4);

--u:for i in 0 to 3 generate

--p:entity work.FA(arch) port map(a,b,c,s,r=>y(i+1));

p0:entity work.FA(arch) port map(a=>a(0),b=>b(0),c=>y(0),s=>s(0),r=>y(1));

p1:entity work.FA(arch) port map(a=>a(1),b=>b(1),c=>y(1),s=>s(1),r=>y(2));

p2:entity work.FA(arch) port map(a=>a(2),b=>b(2),c=>y(2),s=>s(2),r=>y(3));

p3:entity work.FA(arch) port map(a=>a(3),b=>b(3),c=>y(3),s=>s(3),r=>y(4));

--end generate;