數位電路/鎖存器

鎖存器是雙穩態多諧振盪器的例子,即具有正好兩個穩定狀態的器件。這些狀態是高輸出和低輸出。鎖存器具有反饋路徑,因此資訊可以由器件保留。因此,鎖存器可以作為儲存器件,並且可以在器件通電時儲存一位資料。顧名思義,鎖存器用於“鎖定”資訊並保持原位。鎖存器與觸發器非常相似,但不是同步器件,並且不像觸發器那樣在時鐘邊沿上執行。

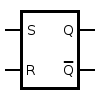

一個SR 鎖存器(置位/復位)是一個非同步器件:它獨立於控制訊號工作,僅依賴於 S 和 R 輸入的狀態。在影像中,我們可以看到一個 SR 鎖存器可以透過兩個具有交叉反饋迴路的 NOR 門來建立。SR 鎖存器也可以由 NAND 門組成,但輸入被交換和取反。在這種情況下,它有時被稱為SR 鎖存器。

當向 SR 鎖存器的置位線施加高電平輸入時,Q 輸出變為高電平(而Q 為低電平)。然而,反饋機制意味著Q 輸出將保持高電平,即使S 輸入再次變為低電平。這就是鎖存器如何用作儲存器件的方式。相反,復位線上的高電平輸入將使Q 輸出變為低電平(而Q 為高電平),有效地復位鎖存器的“記憶體”。當兩個輸入都為低電平時,鎖存器“鎖存”——它保持在先前設定或復位的狀態。

然而,當兩個輸入同時為高電平時,就會出現問題:它被同時告知要產生高Q 和低Q。這會在電路中產生“競爭狀態”——哪個觸發器首先成功更改將反饋到另一個觸發器並斷言自己。理想情況下,兩個門是相同的,這是“亞穩態”的,並且器件將處於未定義狀態,持續時間不確定。在現實生活中,由於製造方法,一個門總是會獲勝,但不可能從裝配線上預測它對特定器件將是哪個。因此,S = R = 1 的狀態是“非法的”,不應該進入。

| S | R | Q | Q | |

|---|---|---|---|---|

| 0 | 0 | 鎖存 | ||

| 0 | 1 | 0 | 1 | |

| 1 | 0 | 1 | 0 | |

| 1 | 1 | 亞穩態 | ||

當器件通電時,會發生類似的情況,因為兩個輸出Q 和Q 都為低電平。同樣,由於兩個門之間的差異,器件將很快退出亞穩態,但無法預測Q 和Q 中哪個最終會變為高電平。為了避免虛假操作,您應該始終在使用 SR 觸發器之前將它們設定為已知初始狀態——您不能假設它們將初始化為低電平狀態。

在某些情況下,可能需要規定鎖存器何時可以和不可以鎖存。門控 SR 鎖存器是對 SR 鎖存器的簡單擴充套件,它提供了一個使能線,該線必須驅動為高電平才能鎖存資料。即使現在需要控制線,SR 鎖存器也不是同步的,因為如果使能線長時間保持高電平,則輸入可以更改輸出。(注意:如果時鐘提供給控制線,則門控 SR 鎖存器被稱為SR 觸發器,因為輸出僅在時鐘的邊沿觸發時才改變。[1])

當使能輸入為低電平時,則 AND 門的輸出也必須為低電平,因此Q 和Q 輸出保持鎖存到先前的資料。只有當使能輸入為高電平時,鎖存器狀態才能改變,如真值表所示。當使能線被斷言時,門控 SR 鎖存器在操作上與 SR 鎖存器相同。

使能線有時是時鐘訊號,但通常是讀或寫選通。

| 使能 | S | R | Q | Q | |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 鎖存 | ||

| 0 | 0 | 1 | 鎖存 | ||

| 0 | 1 | 0 | 鎖存 | ||

| 0 | 1 | 1 | 鎖存 | ||

| 1 | 0 | 0 | 鎖存 | ||

| 1 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 1 | 0 | |

| 1 | 1 | 1 | 亞穩態 | ||

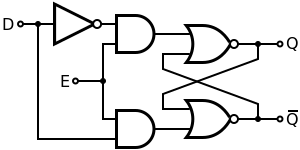

D 鎖存器(D 代表“資料”)或透明鎖存器是對門控 SR 鎖存器的簡單擴充套件,它消除了無效輸入狀態的可能性。

由於門控 SR 鎖存器允許我們在不使用S 或R 輸入的情況下鎖存輸出,我們可以透過使用互補驅動器驅動置位和復位這兩個輸入來刪除其中一個輸入:我們刪除一個輸入並自動使其成為剩餘輸入的反相。

只要使能線為高電平,D 鎖存器就會輸出D 輸入,否則輸出將是使能輸入上次為高電平時D 輸入的值。這就是它也被稱為透明鎖存器的原因——當使能被斷言時,鎖存器被稱為“透明”——訊號直接透過它傳播,就好像它不存在一樣。

| 使能 | D | Q | Q | |

|---|---|---|---|---|

| 0 | 0 | 鎖存 | ||

| 0 | 1 | 鎖存 | ||

| 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 0 | |

D 鎖存器通常用於積體電路的 I/O 埠,並且可以作為分立器件使用,通常是多封裝的。例如,74HC75 是 7400 系列 IC 的一部分,包含四個獨立的 D 鎖存器。