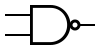

數位電路/與非邏輯

外觀

< 數位電路

就像與非門一樣,與非門被稱為“通用門”,可以組合起來形成任何其他型別的邏輯閘。如今,積體電路不再完全由單一型別的門構成。相反,EDA工具被用來將邏輯電路的描述轉換為複雜門的網路列表(標準單元)或電晶體(全定製方法)

這是一個與非門:簡單來說,只使用一個與非門就可以實現它。

| 目標門 | 與非門構造 | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||

| |||||||||||||||||

非門是由連線與非門的輸入端實現的。由於與非門相當於與門後接非門,因此連線與非門的輸入端只留下了非門部分。

| 目標門 | 與非門構造 | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

|

| |||||||||

| ||||||||||

與門是由一個與非門後接一個非門實現的,如下所示。這相當於一個非與非門,即與門。

| 目標門 | 與非門構造 | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||

| |||||||||||||||||

如果觀察與非門的真值表,可以看到如果任何一個輸入為0,則輸出將為1。然而要成為或門,如果任何一個輸入為1,則輸出也必須為1。因此,如果輸入被反轉,則任何高輸入都會觸發高輸出。

| 目標門 | 與非門構造 | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||

| |||||||||||||||||

與非門只是一個輸出被反轉的或門。

| 目標門 | 與非門構造 | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||

| |||||||||||||||||

異或門可以使用四個與非門構建,實現表示式(A與非N)與非(B與非N),其中N=A與非B。這種結構的傳播延遲是單個與非門的3倍,並使用四個門。

| 目標門 | 與非門構造 | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||

| |||||||||||||||||

或者,可以透過考慮析取正規化來實現異或門,並注意根據德摩根定律,與非門是輸入反轉的或門。這種結構使用五個門而不是四個門。

| 目標門 | 與非門構造 |

|---|---|

|

|

異或非門是透過考慮析取正規化來實現的,並注意根據德摩根定律,與非門是輸入反轉的或門。這種結構的傳播延遲是單個與非門的3倍,並使用五個門。

| 目標門 | 與非門構造 | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||

| |||||||||||||||||

或者,可以使用4門版本的異或門與一個反轉器。這種結構的傳播延遲是單個與非門的4倍(而不是3倍)。

| 目標門 | 與非門構造 |

|---|---|

|

|

- 與非邏輯。與與非門一樣,與非門也是通用門。