數位電子學/暫存器

定義暫存器的方法; 暫存器是比鎖存器更復雜的資料儲存裝置。暫存器是一組適合用於儲存二進位制資訊的二進位制單元。一組級聯的觸發器用於儲存相關的位資訊,稱為暫存器。

在某些情況下,可能希望規定鎖存器何時可以鎖存和何時不能鎖存。門控 SR 鎖存器 是 SR 鎖存器的一個簡單擴充套件,它提供了一個使能 線,該線必須被拉高才能鎖存資料。即使現在需要一個控制線,SR 鎖存器也不是同步的,因為即使在使能脈衝的中間,輸入也會改變輸出。

當使能 輸入為低時,AND 門的輸出也必須為低,因此Q 和 Q 輸出保持鎖存到先前的資料。只有當使能輸入為高時,鎖存器的狀態才會改變,如真值表所示。當使能線被斷言時,門控 SR 鎖存器的操作與 SR 鎖存器相同。

使能 線有時是一個時鐘訊號,但通常是一個讀或寫 選通.

使能 S R Q Q 0 0 0 鎖存 0 0 1 鎖存 0 1 0 鎖存 0 1 1 鎖存 1 0 0 鎖存 1 0 1 0 1 1 1 0 1 0 1 1 1 亞穩態

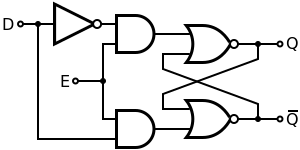

D 鎖存器(D 代表“資料”)或透明鎖存器 是門控 SR 鎖存器的簡單擴充套件,它消除了無效輸入狀態的可能性。

由於門控 SR 鎖存器允許我們在不使用S 或R 輸入的情況下鎖存輸出,我們可以透過用互補驅動器驅動設定 和復位 輸入來刪除一個輸入:我們刪除一個輸入並自動使其成為另一個輸入的逆。

D 鎖存器在使能 線為高時輸出“D”輸入,否則輸出為使能 輸入上次為高時的D 輸入。這就是為什麼它也被稱為透明鎖存器——當使能 被斷言時,鎖存器被稱為“透明”——它的訊號直接透過它傳播,就好像它不存在一樣。

使能 D Q Q 0 0 鎖存 0 1 鎖存 1 0 0 1 1 1 1 0

D 鎖存器通常用在積體電路的 I/O 埠,並且可以作為分立器件獲得,通常是多路封裝的。例如 74HC75,它是 7400 系列 IC 的一部分,包含四個獨立的 D 鎖存器。

T 觸發器 是一種裝置,如果T 輸入被斷言,則每次觸發時都會交換或“切換”狀態,否則它會保持當前輸出。這種行為由特徵方程描述

並且可以用以下表格中的任何一個來描述

|

|

當T 保持為高電平時,觸發器將時鐘頻率除以 2;也就是說,如果時鐘頻率為 4 MHz,則從觸發器獲得的輸出頻率將為 2 MHz。這種“除以”特性在各種型別的數字 計數器 中都有應用。T 觸發器也可以使用 JK 觸發器(J & K 引腳連線在一起並充當 T)或 D 觸發器(T 輸入和Qprev 透過一個異或門連線到D 輸入)構建。

JK 觸發器是對 SR 觸發器的一個簡單改進,其中狀態 J=K=1 並不被禁止。它的工作原理與 SR FF 相同,其中 J 用作設定輸入,K 用作復位。唯一的區別是,對於以前“禁止的”組合 J=K=1,此觸發器現在執行一個動作:它反轉其狀態。由於 JK 觸發器在所有條件下的行為都是完全可預測的,因此它是大多數邏輯電路設計中首選的觸發器型別。但仍然存在一個問題,即在實際測試電路時,兩個輸出都相同。這是由於在每次傳播延遲完成時內部都會發生切換。主要的解決辦法是使用主從式 JK 觸發器,此 FF 透過合併的脈衝時鐘功能來覆蓋自迴圈(內部)重複切換。

| J | K | Qnext | 註釋 | |

|---|---|---|---|---|

| 0 | 0 | Qprev | 保持狀態 | |

| 0 | 1 | 0 | 復位 | |

| 1 | 0 | 1 | 設定 | |

| 1 | 1 | Qprev | 切換 |

| Q | Qnext | J | K | 註釋 | |

|---|---|---|---|---|---|

| 0 | 0 | 0 | X | 保持狀態 | |

| 0 | 1 | 1 | X | 設定 | |

| 1 | 0 | X | 1 | 復位 | |

| 1 | 1 | X | 0 | 保持狀態 |