可程式設計邏輯/FPGA

FPGA 代表 “現場可程式設計門陣列”,是一種在“現場”可程式設計(和可重新程式設計)的 VLSI 型別。FPGA 可以透過使用 HDL 進行程式設計,這些程式從主機計算機系統下載到 FPGA。

現場可程式設計門陣列 (FPGA) 是一種半導體器件,包含可程式設計邏輯元件和可程式設計互連。可程式設計邏輯元件可以被程式設計為複製基本邏輯閘的邏輯功能,例如 AND、OR、XOR、NOT 或更復雜的組合功能,例如解碼器或簡單的數學函式。在大多數 FPGA 中,這些可程式設計邏輯元件(或 FPGA 行話中的邏輯塊)還包括儲存器元件,這些元件可能是簡單的觸發器或更完整的儲存器塊。

可程式設計互連的層次結構允許 FPGA 的邏輯塊根據系統設計人員的需要進行互連,有點像一個單晶片可程式設計麵包板。這些邏輯塊和互連可以在製造過程之後由客戶/設計人員進行程式設計(因此被稱為“現場可程式設計”,即在現場可程式設計),以便 FPGA 可以執行所需的任何邏輯功能。

FPGA 通常比其專用積體電路 (ASIC) 對手速度慢,不能處理如此複雜的設計,並且功耗更大。但是,它們有幾個優點,例如更短的上市時間、能夠在現場重新程式設計以修復錯誤以及更低的非經常性工程成本。供應商可以銷售他們 FPGA 的更便宜、更不靈活的版本,這些版本在設計提交後無法修改。這些設計的開發是在普通 FPGA 上進行的,然後遷移到更類似 ASIC 的固定版本。複雜的可程式設計邏輯器件 (CPLD) 是另一種選擇。

FPGA 的應用包括 DSP、軟體定義無線電、航空航天和國防系統、ASIC 原型設計、醫學成像、計算機視覺、語音識別、密碼學、生物資訊學、計算機硬體模擬以及越來越多的其他領域。FPGA 最初作為 CPLD 的競爭對手而出現,並在類似的空間中競爭,即用於 PCB 的粘合邏輯。隨著其尺寸、功能和速度的提升,它們開始接管越來越多的功能,以至於現在一些被當作片上系統 (SOC) 來銷售。

FPGA 特別適用於可以利用其架構提供的巨大並行性的任何領域或演算法。其中一個領域是破解密碼,特別是對密碼演算法進行暴力攻擊。

FPGA 也廣泛用於系統驗證,包括矽前驗證、矽後驗證和韌體開發。這使得晶片公司可以在工廠生產晶片之前驗證其設計,從而縮短了上市時間。

應用電路必須對映到具有足夠資源的 FPGA。

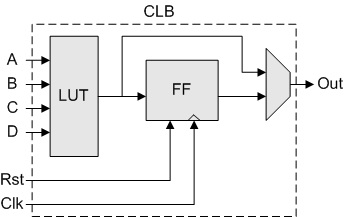

典型的 FPGA 邏輯塊由一個 4 輸入查詢表 (LUT) 和一個觸發器組成。

只有一個輸出,它可以是暫存器化的或非暫存器化的 LUT 輸出。邏輯塊有四個 LUT 輸入和一個時鐘輸入。由於時鐘訊號(以及通常其他高扇出訊號)通常透過商用 FPGA 中的專用專用路由網路進行路由,因此它們和其他訊號分別進行管理。

每個輸入都可以從邏輯塊的一側訪問,而輸出引腳可以連線到邏輯塊右側和下方的通道中的路由線。

每個邏輯塊輸出引腳可以連線到與其相鄰的通道中的任何一條佈線段。

同樣,I/O 焊盤可以連線到與其相鄰的通道中的任何一條佈線段。例如,晶片頂部的 I/O 焊盤可以連線到其正下方水平通道中的任何 W 根線(其中 W 是通道寬度)。

通常,FPGA 路由是未分段的。也就是說,每個佈線段只跨越一個邏輯塊,然後在開關盒中終止。透過開啟開關盒中的一些可程式設計開關,可以構建更長的路徑。為了獲得更高的互連速度,一些 FPGA 架構使用跨越多個邏輯塊的更長的路由線。

每當垂直通道和水平通道相交時,就會有一個開關盒。在這種架構中,當一根線進入開關盒時,有三個可程式設計開關允許它連線到相鄰通道段中的另外三根線。這種架構中使用的開關模式或拓撲稱為平面或基於域的開關盒拓撲。在這種開關盒拓撲中,軌道編號為 1 的線只連線到相鄰通道段中軌道編號為 1 的線,軌道編號為 2 的線只連線到其他軌道編號為 2 的線,依此類推。下圖說明了開關盒中的連線。

為了定義 FPGA 的行為,使用者提供硬體描述語言 (HDL) 或原理圖設計。常見的 HDL 是 VHDL 和 Verilog。然後,使用電子設計自動化工具生成技術對映的網表。然後,網表可以使用稱為佈局佈線的過程(通常由 FPGA 公司的專有佈局佈線軟體執行)擬合到實際的 FPGA 架構。使用者將透過時序分析、模擬和其他驗證方法驗證對映、佈局和佈線結果。一旦設計和驗證過程完成,生成的二進位制檔案(也使用 FPGA 公司的專有軟體)將用於(重新)配置 FPGA。

在典型設計流程中,FPGA 應用開發人員將在設計過程中的多個階段對設計進行模擬。最初,透過建立測試平臺來刺激系統並觀察結果,對 VHDL 或 Verilog 中的 RTL 描述進行模擬。然後,在綜合引擎將設計對映到網表之後,將網錶轉換為門級描述,並在此處重複模擬以確認綜合過程沒有錯誤。最後,設計在 FPGA 中佈局,此時可以新增傳播延遲,並使用這些值反向註釋到網表上再次執行模擬。

為了降低使用 HDL(與等效的組合語言相比)進行設計的複雜性,正在採取措施提高設計的抽象級別。Cadence、Synopsys 和 Celoxica 等公司正在推廣 SystemC,它將高階語言與併發模型結合在一起,從而為 FPGA 提供比使用傳統 HDL 更快的設計週期。基於標準 C 或 C++(帶有庫或其他擴充套件以允許並行程式設計)的方法在 Mentor Graphics 的 Catapult C 工具以及 Impulse Accelerated Technologies 的 Impulse C 工具中找到。Annapolis Micro Systems, Inc. 的 CoreFire 設計套件和 National Instruments LabVIEW FPGA 提供了一種用於高階設計輸入的圖形資料流方法。SystemVerilog、SystemVHDL 和 Handel-C(來自 Celoxica)等語言試圖實現相同的目標,但目標是提高現有硬體工程師的生產力,而不是讓 FPGA 更易於現有軟體工程師使用。

現代 FPGA 系列擴充套件了上述功能,包括固定在矽片中的更高階的功能。將這些通用功能嵌入到矽片中可以減少所需的面積,並且與使用基本元件構建它們相比,這些功能可以提高速度。這些示例包括乘法器、通用 DSP 塊、嵌入式處理器、高速 IO 邏輯和嵌入式儲存器。

為了簡化 FPGA 中複雜系統的設計,人們開發了包含預定義複雜功能和電路的庫。這些庫經過測試和最佳化,可以加速設計流程。這些預定義電路通常被稱為 IP 核,可從 FPGA 供應商和第三方 IP 供應商處獲得(通常收費,且通常受專有許可證約束)。其他預定義電路可從開發者社群(例如 OpenCores.org,通常免費,並根據 GPL、BSD 或類似許可證釋出)和其他來源獲得。

SRAM

針對 FPGA 的嵌入式處理器以軟核 IP 的形式提供,用 HDL(如 VHDL 或 Verilog)描述。大多數軟核由 FPGA 供應商的專有設計軟體提供,並針對其特定的器件。