Signetics 2650 & 2636 程式設計/2650 處理器

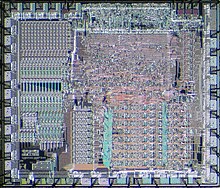

2650 最初由 Signetics 於 1975 年釋出。[1] 這些遊戲機使用的是 2650A,它是一個經過重新設計的版本,體積更小,製造成本更低,並且具有改進的操作餘量。2650A 於 1977 年釋出。[2] 後來,2650B 版本進行了一些設計更改並增加了功能,但這裡我們不關心這些。2650 是用 NMOS 製成的,與 TTL 相容,其許多控制訊號使其易於連線。Adam Osborne 將其描述為非常類似於小型機的裝置,它與 IBM 1130 非常相似。它具有許多獨特的功能

- 32k 位元組地址範圍,組織為四個 8k 位元組頁面。

- 可變長度指令,長度為 1、2 或 3 位元組。

- 單位元 I/O 路徑(標誌和檢測引腳)。

- 包括間接和索引在內的多種定址模式。

- 向量中斷。

- 八級返回地址棧。

- 七個 8 位暫存器。

- 兩個程式狀態位元組。

- 強大的指令集。

2650 有七個通用 8 位暫存器。R0 始終可用,而 R1、R2 和 R3 有兩個組,它們由程式狀態字中的 RS 位選擇。

程式狀態字 (PSW) 是一個特殊用途暫存器,它包含狀態和控制位。它分為兩個位元組,即程式狀態上 (PSU) 和程式狀態下 (PSL)。可以使用tpsu、tpsl、lpsu、lpsl、spsu、spsl、ppsu、ppsl、cpsu 或 cpsl 指令測試、載入、儲存、預置或清除 PSW 位。

|

| ||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||

當將復位脈衝應用於 2650A 時,程式執行將被迫從記憶體地址 0 開始。關於復位後處理器狀態的唯一確定資訊是程式狀態字中的中斷禁止位已清除。由於我們非常不希望發生自發中斷,因此我們的程式應該首先做的第一件事之一就是將其設定為停用它們,直到我們準備好它們為止。“Signetics 2650 初始化應用備忘錄”還建議我們可以將堆疊指標設定為零,並且我們應該將暫存器選擇位設定為已知狀態。[5]

帶進位位和比較位可以設定為在第一次需要它們時的任何狀態。在一個簡單程式中,它們在整個程式中處於相同狀態,這是一個直接的決定。在更復雜的程式中,通常最好先將它們設定為最常用的狀態,然後在需要相反狀態時來回切換。如果帶進位位開啟,則應在第一個算術指令之前適當地初始化進位位。否則,無需初始化進位或任何其他位(條件碼、位間進位或溢位)。 [5]

在 PVI 中發生某些事件會導致它透過將中斷 線置低來向 2650 訊號它需要關注。如果程式狀態字中的中斷禁止位未設定(換句話說,中斷已啟用),則處理器將完成當前指令,然後設定中斷禁止位。然後,PVI 將其中斷向量 3 輸出到資料匯流排,處理器執行 ZBSR(分支到頁面零子程式)到地址 $0003。

中斷服務子程式完成後,應該使用 RETC 或 RETE 指令退出。後者將重新啟用中斷。

2650A 指令集中的所有助記符都是 3 或 4 個字元。前兩個或三個字元指定操作,如果有的話,最後一個字元表示要使用的定址模式(有關詳細資訊,請參閱下一節,定址模式)。2650 的彙編程式碼通常如下所示

loop: lodi,r0 $20 ; load r0 from the byte immediately following, $20

stra,r0 $1F40 ; store r0 in the absolute address $1F40

eorz r0 ; exclusive-or r0 with itself

bctr,un loop ; branch relative, unconditionally, to address specified by 'loop'

有 34 條基本指令

| 傳輸 | LOD | Z,I,R,A | 載入暫存器 |

| STR | Z,R,A | 儲存暫存器 | |

| 算術 | ADD | Z,I,R,A | 加到暫存器 |

| SUB | Z,I,R,A | 從暫存器中減去 | |

| DAR | 十進位制調整暫存器 | ||

| 邏輯 | AND | Z,I,R,A | 按位與到暫存器 |

| IOR | Z,I,R,A | 按位或到暫存器 | |

| EOR | Z,I,R,A | 按位異或到暫存器 | |

| 測試 | COM | Z,I,R,A | 將值與暫存器比較 |

| TM | I | 測試暫存器的掩碼位 | |

| 旋轉 | RRR | 將暫存器向右旋轉一位 | |

| RRL | 將暫存器向左旋轉一位 | ||

| 分支 | BCT | R,A | 如果條件為真,則分支 |

| BCF | R,A | 如果條件為假,則分支 | |

| BRN | R,A | 如果暫存器不為零,則分支 | |

| BIR | R,A | 遞增暫存器,如果它不為零,則分支 | |

| BDR | R,A | 遞減暫存器,如果它不為零,則分支 | |

| ZBR | R | 分支,相對於地址 $0000 | |

| BX | A | 分支,索引 | |

| 呼叫/返回 | BST | R,A | 如果條件為真,則分支到子程式 |

| BSF | R,A | 如果條件為假,則分支到子程式 | |

| BSN | R,A | 如果暫存器不為零,則分支到子程式 | |

| ZBS | R | 分支到子程式,相對於地址 $0000 | |

| BSX | A | 分支到子程式,索引 | |

| RET | C,E | 有條件地從子程式返回。 RETE 還啟用中斷 | |

| 輸入/輸出 | WRT | C,D,E | 這些遊戲機上沒有實現輸入/輸出硬體 |

| RED | C,D,E | ||

| 其他 | HALT | 進入等待狀態,直到處理器復位或中斷 | |

| NOP | 除了獲取和執行此指令之外什麼也不做 | ||

| 程式狀態字 | LPS | U,L | 載入 PSW |

| SPS | U,L | 儲存 PSW | |

| CPS | U,L | 清除 PSW 中的指定位 | |

| PPS | U,L | 預置 PSW 中的指定位 | |

| TPS | U,L | 測試 PSW 中的指定位 |

Signetics 2650 有四種主要的定址方式:暫存器、立即、相對和絕對。此外,間接和索引定址可以與其中一些方式組合使用。

所有暫存器到暫存器的指令都是 1 位元組長,並使用 R0 作為第一個運算元,而另一個運算元可以是 R0、R1、R2、R3 中的任何一個。

lodz r3 ; load r0 from r3

addz r2 ; r0 = r0 + r2

lodz r0 ; not very useful!

eorz r0 ; exclusive-or r0 with itself

; very useful! A one byte instruction for r0 = 0

在立即定址中,第一個運算元(可以是任何暫存器)在指令旁邊指定;後面跟著另一個運算元的值,該運算元隱式地必須是一個常量。所有立即定址指令都是 2 位元組長。

lodi,r2 $20 ; r2 = 32

subi,r0 8 ; r0 = r0 - 8

iori,r1 %00100000 ; set bit5 of r1

comi,r3 15 ; compare r0 to 15

在絕對定址中,第一個運算元(可以是任何暫存器(但請參閱下面的索引定址中的異常))在指令旁邊指定。第二個引數指定另一個運算元所在的記憶體位置的絕對地址。

在相對定址中,第一個運算元(可以是任何暫存器)在指令旁邊指定。第二個引數指定另一個運算元所在的記憶體位置。這個第二個引數是相對於當前地址的相對位移,可以是 -64 到 +63 之間的任何值。在實踐中,我們不將此值指定為數字。它通常採用標籤的形式,彙編器會為我們進行計算。如果標籤距離太遠,彙編器將生成錯誤訊息。相對定址也用於分支指令,以跳轉到附近的記憶體位置。

lodr,r2 number ; r2 = 42

bctr,un next ; branch to next

number: db 42 ; define a data byte = 42

next: addi,r2 53

當使用索引定址時,有效地址透過將指定索引暫存器的內容新增到地址欄位來計算。加法使用索引暫存器中的值作為 8 位正數。

lodi,r2 5

loda,r0 $1F00,r2 ; r0 = contents of address $1F05

請注意,第一個引數始終是 r0。一些彙編器可能允許從程式碼中省略它,但為了可讀性,應儘可能包含它。

另外兩個選項允許在索引暫存器新增到基地址之前自動遞減或自動遞增。

lodi,r2 5

loda,r0 $1F00,r2+ ; r0 = contents of address $1F06

lodi,r3 $A6

loda,r0 $1000,r3- ; r0 = contents of address $10A5

索引只能與絕對定址一起使用。它不能與分支指令一起使用,但有兩個特殊指令用於此目的。它們是 BXA(分支索引,絕對)和 BSXA(分支到子程式索引,絕對)。自動遞增和自動遞減不能與它們一起使用,並且必須指定暫存器 R3 作為索引暫存器。

間接定址意味著指令的引數地址不是由指令本身指定的,而是引數地址將在指令指向的兩個位元組中找到。間接定址模式由星號 (*) 表示。

pointer dw $0F00 ; in most cases this would be an address in RAM, i.e. a variable

.....

loda,r1 *pointer ; r1 = contents of $0F00

間接定址也可以與相對定址一起使用,但由於這些控制檯中程式碼是從 ROM 中執行的,並且 RAM 地址通常距離太遠而無法進行相對定址,因此沒有明顯的用途。當代碼空間非常寶貴時,會出現一個例外。

:bar equ $1F0E 0000 066A : lodi,r2 $6A 0002 CE1F0E : stra,r2 bar 0005 0D1F0E :foo loda,r1 bar 0008 0BFC : lodr,r3 *foo+1 ; load r3 indirectly from $0006, i.e. $1F0E

最後兩個指令都從bar載入一個暫存器,但最後一個指令只使用了兩個位元組而不是三個位元組。

當索引和間接定址一起使用時,索引暫存器的值將新增到間接地址,而不是新增到指令的地址欄位中的值。

有關更多詳細資訊,請查閱Signetics 2650 使用者手冊,該手冊以完整 pdf 格式或針對程式設計師的 html 縮寫版提供。

- ↑ 微型計算機文摘 (PDF). 庫比蒂諾,加利福尼亞州:微型計算機協會。2 (1): 1–3. 1975 年 7 月 http://bitsavers.trailing-edge.com/magazines/Microcomputer_Digest/Microcomputer_Digest_v02n01_Jul75.pdf. 存檔 (PDF) 於 2014 年 2 月 1 日從原文中. 檢索於 2021 年 12 月 4 日.

{{cite journal}}: Cite has empty unknown parameter:|1=(help); Invalid|url-access=2021 年 12 月 4 日(help); Missing or empty|title=(help) - ↑ "Signetics 2650: An IBM on a Chip". CPUshack 博物館. 2016 年 10 月 16 日. 檢索於 2021 年 12 月 5 日.

{{cite web}}: Check date values in:|date=(help) - ↑ 奧斯本,亞當 (1978). 微型計算機導論 (PDF). 伯克利,加利福尼亞州:奧斯本與合夥人。p. 736. ISBN 0-931988-15-2. 檢索於 2021 年 11 月 4 日.

- ↑ 2650 系列微處理器資料手冊 (PDF). 飛利浦. 檢索於 2021 年 11 月 4 日.

- ↑ a b Signetics 應用備忘錄 MP51 - 2650 初始化 (PDF). 飛利浦. 檢索於 2021 年 11 月 4 日.