時鐘和資料恢復/簡介

為了透過一定距離傳輸數字資訊,需要將其序列化(無論是在透過一根引導介質(如電纜、光纖等)傳輸時,還是在無線傳輸時)。

數字資訊通常被編碼以進行錯誤檢測和糾正。

編碼後的位元流會攜帶它自己的時鐘資訊。

時序資訊,即時鐘,本質上是由傳輸訊號的電平躍遷攜帶的。

在傳輸過程中,產生的訊號會受到噪聲和傳輸介質傳輸函式的影響,並可能導致資訊內容的不希望的損壞。

在接收端,訊號儘可能恢復(均衡並濾除噪聲)。

然後提取時序資訊,並重新生成位元流。

在資料接收器內部執行這些最後功能的電子電路稱為時鐘和資料恢復塊 (= CDR)。

從接收訊號中恢復時鐘訊號的操作不可避免地會受到一些退化的影響。由於均衡/噪聲濾波不良以及恢復的時鐘相對於恢復的脈衝的同步不完美,可能會在隨後的編碼位元流的再生中出現錯誤。

資料和時鐘在它們一起傳輸的過程中,受噪聲和符號間干擾的影響,並獲得了

- 兩者:由於物理傳輸時間和提取過程,不可避免的延遲;

- 時鐘:一些時序誤差(= 相位調製,稱為抖動)

- 重新生成的位:一些錯誤的位,具有(非常)低的機率,或者換句話說,位元誤位元速率非常低(例如 <10−19)。

使用複雜的時鐘提取電路可以將抖動降至最低,但無法消除。

另一方面,在網路拓撲中,總是存在一些點,這些點將來自同一個時鐘的訊號,並在不同的傳輸路徑上積累了不同的抖動,必須再次組合在一起。

為了吸收抖動差異,使用了一個彈性緩衝器(一種特殊的緩衝記憶體)。

- 資訊儲存在記憶體中,以寫入記憶體單元中的位的形式儲存。

- 大多數記憶體都是由一組具有唯一地址的單元組成。每組單元容納一個記憶體字,該記憶體字由 8 位組成,或者由 8 位的整數倍組成。每組 8 位資訊構成一個位元組。

- 一個檔案[註釋 2](即記憶體一部分的內容)必須“傳輸”以使其資訊內容在其他地方可用。“傳輸”意味著透過電子方式傳送並在另一個記憶體的類似部分內複製。

- 記憶體透過與每個字一樣寬的並行匯流排儲存並輸出其內容。一個字的位可以在一個總線上同時並行傳輸,總線上有與記憶體匯流排一樣多的連結(通常還有一個連結來傳輸對每個後續字的位進行計時 的時鐘)。

- 這被稱為並行傳輸。對每個字內容傳輸進行計時 的時鐘的頻率等於

- 當連結上的位元率超過一定限度時,並行傳輸變得不切實際。

- (並行)連結將資訊位作為電磁訊號(電訊號或光訊號)攜帶。

- 並行連結的物理長度永遠不會相同,長度可以用一個資訊位透過連結所需多少個時鐘週期來衡量。

- 如果並行路徑經歷了很大的延遲差異,則連結末端的單個時鐘可能無法將給定字的所有位一起載入到接收記憶體中。

- 不同的並行路徑之間的延遲差異可能導致給定字的位(在同一時間傳送)在接收端以不同的時鐘週期接收。

- (距離差異包括每個路徑(傳送和接收)的電子電路中的不同延遲。)

- 並行傳輸受到並行路徑的長度差異的限制。[註釋 3]

- 並行傳輸在以下兩種情況下是可行的:

- 不同的路徑具有小於位間隔四分之一的延遲差異,以及

- 匯流排的連線可以變得非常便宜。

- 或者,時鐘速度可以乘以並行位的數量,並且一個字的位可以在單個傳輸線上一個接一個地傳送,時間段等於並行傳輸的一個時鐘週期。

- 當距離太長或成本可以降低時,使用序列傳輸。

- 網路中的裝置在其處理核心內部使用並行處理,但透過一個或多個序列鏈路連線到外部。

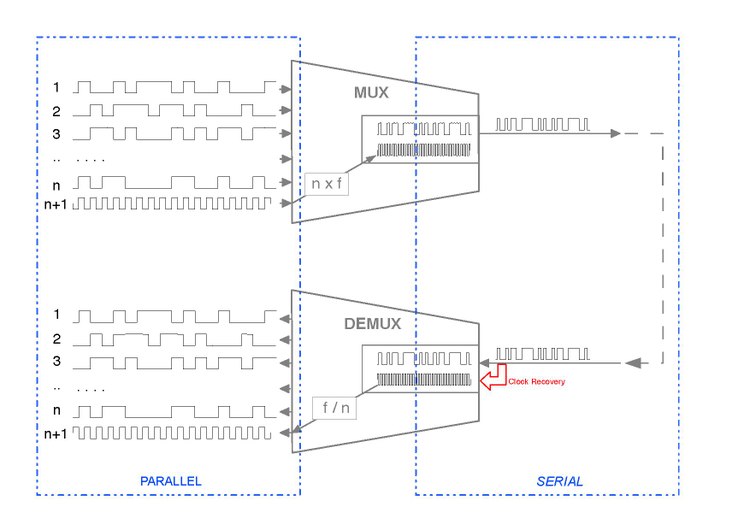

- 因此,在傳送端可以識別一些電路,這些電路將並行轉換為序列(複用器),以及一些電路在另一端將序列轉換為並行(解複用器)。

- 下圖實際上描繪了序列鏈路的一個完整單向部分,該部分等效於描繪並行到序列介面的兩個方向。

- 該圖也有助於指出(以紅色顯示)需要重新生成組合訊號/時鐘的點。第一個基本操作是從組合的時鐘和資料訊號中恢復時鐘,這個操作是本書的主題。

本書探討了 CDR(時鐘和資料恢復)電路,但只分析和研究了它們所包含的 PLL(鎖相環)。

這些 PLL 是 CDR 的重要部分(= 用於時鐘恢復,= CDR 的 CR 部分)。

CDR 的 DR(資料恢復)部分沒有深入研究,這裡只研究適合時鐘恢復功能的 PLL。

用於其他應用的 PLL,例如移動物體的位置檢測或非調製訊號的識別,在這裡不予考慮。

近年來,由於行動電話的爆炸式增長,頻率合成器內部的 PLL(它們不是 CDR)取得了長足的進步。可以說,如今 PLL 的絕大部分應用都體現在頻率合成器中。

CDR 中 PLL 的特殊之處,是資訊位元與其時鐘直接“混合”成唯一的脈衝串流。通常,NRZ 傳輸資訊位元可以完美地完成任務。對於其他傳輸通道,不同的位元和時鐘“編碼”可以更好地最佳化整體效能,並增加再生所需的距離。

在所有情況下,由於資訊位元本質上的“不可預測性”,混合的串流的頻譜不會在固定頻率處出現整齊的譜線,而是會以大瓣的形式散佈;其電平躍變不會發生在每個可能的時刻,而是在其中的部分時刻隨機發生。為了簡化數學,本書中使用了“躍變密度”的概念。此外,這些躍變發生時會相對於理想位置抖動,因為通道失真和噪聲的存在。

相反,頻率合成器鎖定的訊號是規則的週期性波形,其頻譜接近於具有噪聲邊帶的強譜線。其電平躍變以 100% 的密度發生。

時鐘額外費用

[edit | edit source]與資料一起傳輸的時鐘

[edit | edit source]用於序列傳輸時逐個釋放資料位元的時鐘訊號必須與資料位元一起傳輸,並且必須在到達時首先恢復,以便隨後可以對接收到的資料位元進行再生。

為了有效地利用(一個良好的百分比)通道容量,實際的序列鏈路需要一個時鐘,該時鐘可以在到達點正確識別每個資料脈衝。 [2]

當資料以最簡單的方式(NRZ)傳輸時,每個符號都是一個脈衝(0 或 1),其持續時間正好等於關聯時鐘的一個週期。關聯時鐘在(並且可以從)兩個後續符號之間的“躍變”(從 1 到 0 或從 0 到 1 的電平變化)中可見。不幸的是,兩個符號之間並不總是存在躍變。如果躍變發生的頻率不夠高(躍變密度,執行長度,...),那麼就不可能恢復與接收到的資料相關的時鐘。

火車類比

[edit | edit source]- 為了闡明這個概念,可以使用一個簡單的類比,即火車運輸,其中在每個給定的正常乘客(資料位元)組中都會增加一些額外的乘客。

- 這些額外的乘客將在到達後協助其他人,但會減少可供原始乘客使用的座位數量,這些乘客為所有人支付費用(使用減少數量座位的付費乘客組代表了這個類比中的有效載荷)。

- 恢復的時鐘對於在乘客下火車時再生資料乘客是必要的。這個(恢復的)時鐘對於完全再生每個資料位元乘客是必要的。沒有其他時鐘可以做到這一點。

- 在所有執行到達(接收器)時完成其任務的額外乘客中,有些乘客協助時鐘恢復,但有些乘客可能存在是為了糾正狀態最差的乘客,這些乘客可能以糟糕的狀態到達並且被錯誤地再生(位元錯誤糾正),還有一些乘客可能存在於這些任務型別的組合中(幀,等等)。[3]

基本理論

[edit | edit source]基於夏農-哈特利定理的基本理論沒有明確地解決時鐘恢復問題,因為其綜合公式僅對

- 線性系統以及

- 最通用和最隨機的噪聲型別 (高斯噪聲)

- 該定理也沒有考慮到完成接收位元的完全再生所需的總可用時間在實踐中非常短。 [4]

但“通道容量定理”有效性的假設表明

- 連續傳輸 比突發傳輸更接近理論極限,並且

- 實際系統需要複雜的編碼方案才能向理論極限改進 [5]。

這個基本公式的意義遠遠超出了其陳述的假設。

事實上,它之所以流行,是因為它提供了對現實的理解,在現實中,頻寬和噪聲並非以數學精度已知,並且許多量之間的關係與線性關係有很大偏差。

當應用於非線性現象時,它提供了良好的近似值,例如源於影響接收訊號躍變的相位噪聲的位元錯誤率(即時鐘抖動)。

- 惡化時鐘的相位噪聲(時鐘本質上是一個方波,受噪聲影響,噪聲只不過是抖動)會增加位元錯誤率 BER(即降低理論通道容量 C),就像在夏農-哈特利公式中降低信噪比(S/N)一樣。

- 嚴格來說,該公式只有在噪聲為高斯噪聲時才產生準確的結果。但高斯噪聲是最隨機的噪聲,恢復的時鐘相位噪聲來自許多不同干擾的累積。可以理解,即使透過(略微)不同的數量,兩種噪聲都會產生更高的 BER(即兩種噪聲都會降低通道容量 C)。

實際的額外費用

[edit | edit source]實際為了讓時鐘與關聯資料一起傳輸而付出的成本(以位元率、通道頻寬或通道容量衡量)有多大?

夏農-哈特利定理沒有說明如何設計一個滿足實際情況給定要求的系統,並且沒有提供簡潔的公式供設計工程師使用,因此實施任務就交給了他們。

所有傳輸裝置的設計都與它們可能使用過的最長線路長度相容。

在所有這些裝置中,時鐘恢復電路的設計使得恢復的時鐘的抖動保持足夠小,以不產生或只產生位元錯誤率的微小增加,即使連線到它們指定的w:通訊通道的最長線路也是如此。

換句話說,時鐘抖動對總的等效 S/N 的貢獻可以忽略不計,但這需要以減少乘客座位數量為代價,即降低淨位元率,這反過來又等同於減少可用頻寬 B。

在大多數實際情況下,為了獲得無錯誤的時鐘恢復而付出的通道容量降低範圍從最大大於 10%(突發傳輸)到幾百分比(連續傳輸)。 [6]

本書旨在為理解、研究和設計用於 CDR 應用的 PLL 系統提供良好的理論基礎。

CDR 的 PLL 是一個單位反饋系統,因為輸出(恢復的時鐘)應該儘可能接近輸入(嵌入到傳入脈衝流中的時鐘),除了對後者的高頻分量進行抑制。

完全由線性行為的電路塊組成的 CDR 可以很好地用線性數學模型來描述,即用以時間為自變數的線性微分方程及其拉普拉斯或傅立葉變換來描述。

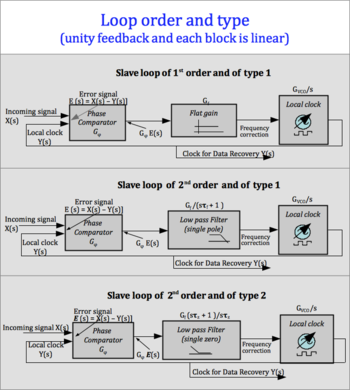

任何 CDR 的 PLL 都可以用三種“控制迴路結構”(= 架構,在框圖意義上)中的一個來描述。

它們可以僅透過其階數和型別這兩個數字來識別。下圖根據它們的線性模型識別了三種架構。

在實踐中用所有線性模組實現的結構是

具有一個或多個硬非線性的 CDR 不能用線性數學模型充分描述。(需要針對每個不同的訊號電平重新計算額外的模擬)。

- 廣泛(且通常不可避免)使用本質上非線性的相位比較器(bang-bang)導致使用更寬容和更穩健的架構。(bang-bang 相位檢測器的增益不是固定的,而是隨其輸入端的相位差而變化)。

這些結構仍然可以透過對應線性迴路的階數和型別來識別。

並且在實踐中

- 一階、型別一的迴路(與 1.1. 完全相同),用於“相位對準器”和“終點”的應用。

- 二階、型別二的迴路(如果使用線性相位比較器,則此結構不受歡迎),用於“再生器”和“終點”的應用。對線性(2.2)架構(所有模組都是線性的)的詳細分析對於理解其使用 bang-bang 相位檢測器的實際應用仍然非常重要。

在本書中,對於所有列出的情況(1.1.、1.2. 和 2.2.)

- 提供了線性模型(復變數 或 的函式,以及實變數 的函式),以便可以研究“小訊號”條件下的操作(抖動容限、抖動傳遞、噪聲傳遞、單位階躍響應等)。

- 每個 PLL 模組的

- 以及整個系統的

- 使用透過數值模擬獲得的結果,調查了線性模型適用性超出範圍的重要點。

- 已經開發了幾個版本的模擬程式,可以根據要求提供 [7] 。

- ↑ 並行:每個位在字中使用一條傳輸線,所有字的位同時傳輸

- 並行總是同步的(即,還有一條傳輸線用於標識每個字的時鐘)

- ↑ 檔案,在檔案的意義上,詞源 1,4: “儲存裝置上的資料聚合,由名稱識別。”

- ↑ 除非使用額外的(並且複雜的)技巧,否則並行傳輸不可能超過一定距離。 為了使偏移的位流重新同步,需要在傳送階段在每個位流中插入冗餘位,以便在接收端可以檢測到幀同步。然後,需要在每條路徑的末端使用緩衝儲存器來使所有並行路徑的位重新同步。已經提出了具有此結構的介面,並且在某些系統中使用。

- ↑ 當並行訊號(包括時鐘)傳輸的多個鏈路在其位速率上相差 50% 或更多時,需要進行序列傳輸,並將時鐘和資料一起編碼在單個鏈路上。當 +/- 25% 可能超過時,建議使用序列傳輸。

需要強調的是,序列傳輸需要在傳輸之前對每個字的 n 位進行多路複用,並在傳輸結束時進行解複用,以並行地顯示每個字的位。序列傳輸的位速率是對應並行傳輸的 n 倍。

序列鏈路的長度不需要與其他鏈路的長度完全匹配。當距離超過幾米時,序列傳輸總是優先於所有型別的傳輸線。即使對於較短的距離,也經常使用序列傳輸。

序列傳輸僅受其傳輸技術可達到的總長度限制。使用光纖這意味著從數百米到一百多公里。

例如:在 1 Gbps 時,參考波長為:- c/(1 GHz) = 3 * 108 m/s / 109 sec-1 = 30 cm.

因此,當並行路徑(在 1 Gbps 下使用)之間的距離差異為 5 釐米或更多時,序列編碼傳輸(在 n 倍 1 Gbps 下,例如,如果並行鏈路為 8,則為 8 Gbps)變得更受歡迎。

如果考慮銅纜或光纖纜(裝置背板或裝置間),由於並行電纜和聯結器的成本更高,因此選擇序列傳輸更有優勢。

- ↑ FED-STD-1037C.PDF, 第 414 頁,共 498 頁

- 傳輸線:構成從一個地方到另一個地方的路徑的所有或部分材料介質或結構,用於引導能量的傳輸,例如電流、磁場、聲波或電磁波。

- 注意:傳輸線的示例包括電線、光纖、同軸電纜、矩形閉合波導和介質板。

- 下載自 http://www.everyspec.com 2017 年 9 月 20 日 星期三

- ↑

- 理想情況下,但僅僅是理想情況下,時鐘可能會沿著一個獨立的平行路徑執行。

- 在評估平行多資料鏈路的距離限制時(在考慮平行時鐘路徑時,這種限制非常相似,就像在本段中一樣),從稍微不同的角度,已經描述了獨立時鐘路徑的缺點 在本介紹頁中。

- ↑ 在實際資料網路中,存在沿著專用平行路徑執行的時鐘(類似於專用火車,舒適且專供時鐘乘客乘坐)。

它們以非常好的狀態到達目的地,然後可以乘坐載有普通乘客的離開列車,這些乘客也到達了同一個車站。

這些乘客組可以利用新的時鐘,比與他們一起旅行的時鐘更乾淨,但只有在由與他們一起旅行並共享相同不適(經歷了相同的失真)的時鐘重新生成之後。 - ↑ 這樣的時間只是終端使用者所經歷的總延遲的眾多因素之一,因此必須將其控制在最小範圍內。

對於許多應用,無論是即時傳輸還是非即時傳輸,網路節點之間的總延遲(其中發生多個時鐘恢復、去幀、第 2 級和第 3 級資料包路由)最好保持在 20 毫秒以下。(例如,終端使用者所經歷的音訊通話的總 延遲 必須保持在 200 毫秒以下)。 - ↑ 麻省理工學院關於夏農極限的新聞文章

- ↑ 為了進行滿意的時鐘恢復,在不同的情況下使用不同的技術。通常,在同一應用程式中存在多種技術,但幾乎所有技術都包括獲取有限數量的線路脈衝並將它們分配給時鐘恢復(和其他)目的。有用的位元率相應降低,因此夏農-哈特利意義上的通道容量也降低。

為了使時鐘與相關資料一起傳播,實際付出的代價(就位元率、通道頻寬或通道容量而言)有多大?

由於數字網路中存在許多不同的解決方案,以及每個解決方案除了時鐘恢復之外可能提供的其他目的,因此答案只能透過一系列可能的值來近似。

還必須考慮,每當資料包下降到 OSIRM 層級階梯的一級以到達底部並變成實際透過物理介質傳輸的脈衝序列時,負載位都會載入額外的開銷位。

每個額外的開銷都有助於建立脈衝序列,使時鐘恢復變得更加容易,即使是最低層新增的開銷主要目的是直接確保時鐘恢復。

在突發傳輸中,每個突發開始處的座位(位元間隔)被拒絕支付乘客。首先傳輸的脈衝序列被選擇以產生大量的過渡,以允許非常快的時鐘恢復。時鐘的鎖相在最短的時間內實現,並且所有後續的資料位都可以正確地重新生成。

在連續傳輸中,沒有這樣的考慮,因為可以分配更長的時間來達到鎖相(傳輸開始事件是一個罕見的事件,其持續時間對整體效率的影響可以忽略不計)。

在非常短的鏈路和頻寬過剩的極端情況下,有時使用 差分曼徹斯特 而不是 NRZ。

差分曼徹斯特應該被視為極端情況。所需的通道頻寬是原來的兩倍,而通道容量沒有增加,以換取出色的時鐘恢復和其他優勢(在接近 0 的頻率處訊號功率極低,以及對極性反轉不敏感,恆定訊號功率,...)。新增乘客的總額外費用為 50%,其中大部分可以歸因於時鐘。

8b/10 編碼 每 8 個位新增兩個額外座位,主要目的是確保時鐘可以在連續傳輸中輕鬆恢復。(在這種情況下,與新增兩個非支付乘客的類比有點混亂,因為 10 位的整體組不是簡單地新增兩個新的位並保留原始的八個位:存在一些加擾。最初的 8 位乘客組在行程中無法識別,但到達時會重新建立)。時鐘的額外費用佔容量降低的 (10-8)/10 = 20%。

64B/66B 傳輸碼 是 8b/10b 的一個更新且開銷更低的版本。它用於 快速乙太網、千兆乙太網 和 10 千兆乙太網 標準。通道容量降低為 (66-64)/66 = 3%,但時鐘只保證每 66 個位有 1 個額外的轉換。時鐘的額外費用可以計算為 1.5%。為了彌補 8b/10b 的一些優勢,它總是與 加擾 一起使用,這在統計上減輕了它在直流平衡、行程長度和過渡密度方面的較低效能。

在大多數實際情況下,為了進行無錯誤時鐘恢復而犧牲的通道容量降低範圍從大於 10%(突發傳輸)到幾個百分點(連續傳輸)。 - ↑ 請求可以郵寄到:plz.pllsmltor.file@gmail.com。模擬程式以迴圈引數和輸入訊號特性作為輸入,並以這些條件下“大訊號”行為的表示作為輸出,例如迴圈採集波形